# PROCEEDINGS

San Luis - Argentina March, 2023

# Welcome

The SPL2023 Organizing Committee, gives you welcome to the **XI Southern Programmable Logic Conference** in San Luis, Argentina.

The conference is organized by Universidad Nacional de San Luis, Argentina, and we aim to provide a high-level international forum for researchers and engineers to discuss recent advances, new techniques and applications in the field of reconfigurable logic technology. The XI edition continues the tradition of the previous one to become the meeting point for the worldwide community in the area.

SPL2023 topics include Embedded Processors and IP Cores, System-on-Chip, Computer Arithmetic, Image Processing and Vision, FPGA Architectures for Specific Applications, Fault Tolerance, Test & Verification, High-Performance Computing, Design Methodologies and Tools, High-Level Abstraction, Reconfigurable Computing, and Hardware/software co-design.

We would like to make a special acknowledgement of the contribution of our distinguished keynote speakers, the session organizers, the reviewers and all the authors. Your participation, and the spirit in which you undertake it, makes SPL2023 more successful.

Finally, we sincerely wish you a pleasant stay and a fantastic memory of San Luis.

Sincerely, Operating Committee

# Institutional sporsonsing

# Operating committee

## **General Chair**

Julio Dondo Gazzano - Universidad Naciona de San Luis (UNSL, Argentina)

## **Program Co-Chairs**

Carlos Vaderrama Sakuyama - Université de Mons, Department of Electronics and Microelectronics (SEMI, Belgica)

Fernando Rincón Calle - Universidad de Castilla-La Mancha (UCLM, España)

## **Proceedings Co-Chairs**

Elias Todorovich - Universidad Nacional del Centro de la Provincia de Buenos Aires (UNICEN, Argentina)

Juan Pablo Soto Barrera - Universidad de Sonora (UNISON, Mexico)

### **Designer Forum Chair**

Cristian Sisterna - Universidad Nacional de San Juan (UNSJ, Argentina)

### **Financial Co-Chairs**

Ricardo Cayssials - Universidad Tecnologica Nacional Bahia Blanca (UTN BHI, Argentina)

Cristian Falco - Universidad Nacional de San Luis (UNSL, Argentina)

### **International Relationship Chair**

Gustavo Suter - Universidad Autónoma de Madrid (UAM, Spain)

### Local Chair

Carlos Federico Sosa Paez - Universidad Nacional de San Luis (UNSL, Argentina)

## **Local Committee**

Diego Costa - Universidad Nacional de San Luis (UNSL, Argentina)

Roberto Kiessling - Universidad Nacional de San Luis (UNSL, Argentina)

## **Publicity Chairs**

Rodrigo Alejandro Melo - indie Semiconductor (Argentina)

Ivana Trento - Universidad Nacional de San Luis (UNSL, Argentina)

## XI Southern Conference on Programmable Logic SPL2023

## Table of Contents Full Papers

- Hardware Acceleration of a CNN-based Automatic Modulation Classifier......1 Sravanth Chebrolu, Srinivas Boppu and Linga Reddy Cenkeramaddi.

- FPGA Implementation of Staggered Cellular Automata for Wave Propagation Simulation......7 Gustavo O. Pereira, Santiago Guzman-Anaya, Henrique G. Moura and Daniel M. Muñoz

- Streamlining FPGA Circuit Design and Verification with Python and py4hw......14 David Castells-Rufas, Gemma Rotger and David Novo.

Open-source SoC-FPGA Platform for Signal Processing.......21 Matías Javier Oliva, Pablo Andrés García, Enrique Mario Spinelli and Alejandro Luis Veiga

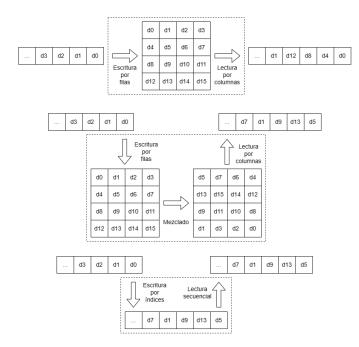

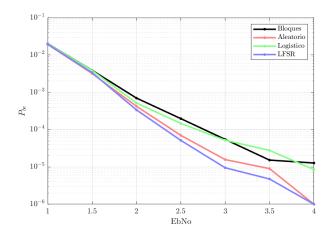

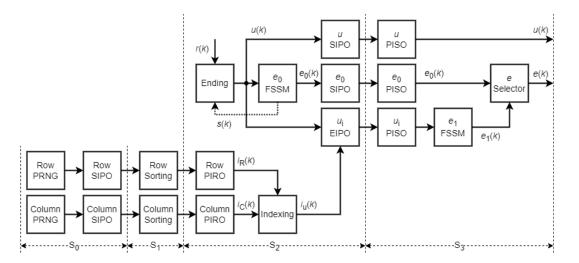

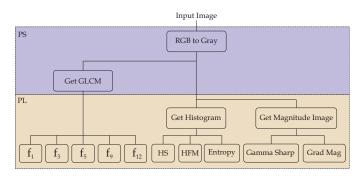

Turbo-Código seguro mediante Interleaver aleatorio variable en el tiempo......27 Raúl Eduardo Lopresti, Maximiliano Antonelli, Jorge Castiñeira Moreira y Luciana De Micco

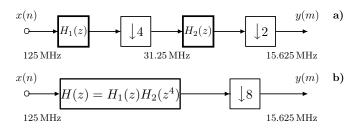

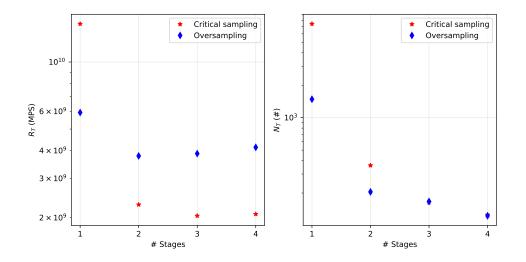

Multi-stage multirate filterbank for FPGA resource optimization.......43 *L. H. Arnaldi*

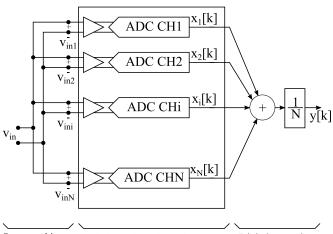

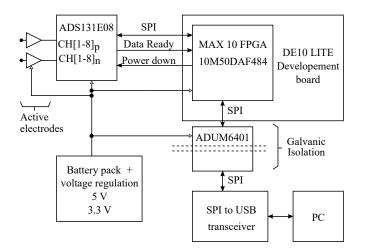

Real-time noise reduction through independent channel averaging for real-time biomedical signal acquisition......49 *Federico Guerrero, Matías Oliva and Enrique Spinelli*

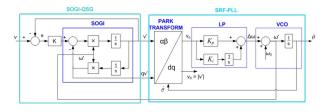

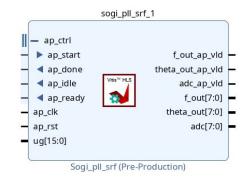

Diseño en VHDL del algoritmo SOGI PLL SRF usando síntesis de alto nivel (HLS)......55 Alejandro Núñez Manquez, Matín Murdocca, Victor Yelpo e Ivana Trento

Paez.

# Hardware Acceleration of a CNN-based Automatic Modulation Classifier

Sravanth Chebrolu \*, Srinivas Boppu\*, Linga Reddy Cenkeramaddi<sup>†</sup>

cs21@iitbbs.ac.in, srinivas@iitbbs.ac.in, linga.cenkeramaddi@uia.no

\*School of Electrical Sciences, Indian Institute of Technology Bhubaneswar (IITBBS), India <sup>†</sup>Department of Information and Communication Technology, University of Agder, Norway

Abstract-Automatic modulation classification (AMC) has found its place in numerous applications, ranging from cognitive radio and adaptive communication to electronic reconnaissance and spectrum interference detection. Several attempts have been made to develop a high-accuracy modulation classifier using machine learning based convolutional neural networks (CNNs). This paper considers one such model, which uses a fixed boundary range empirical wavelet transform and deep CNN, and accelerates the model on the ZCU104 FPGA board to achieve fast classification times. The proposed accelerator can achieve a maximum classification accuracy of 96% for +8 dB signal-to-noise ratio (SNR) radio signals. Compared to similar works, the accelerator performs reasonably well for low SNR ratios ( $\leq +6$  dB). Furthermore, the model is implemented on an edge CPU device (Raspberry Pi), and our accelerator is  $50 \times$  faster than the CPU implementation. Our design achieves a reasonable throughput of 1.8K classifications/sec and a classification time of  $550 \, \mu s$  per sample.

Index Terms—Modulation Classification, Hardware Acceleration, Deep Learning, Convolutional Neural Networks, Vitis AI

#### I. INTRODUCTION

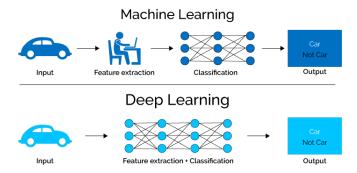

There have been significant advances in wireless communication technologies and their standards recently. Understanding the radio spectrum in an autonomous manner plays an important role in numerous applications, such as electronic warfare, threat analysis in military scenarios, dynamic spectrum access, and spectrum interference detection [1], [2]. For instance, automatically identifying the modulation types of received signals allow the receiver to demodulate the signal; thus, the development of an efficient algorithm for modulation identification, also called Automatic modulation classifier (AMC), is the priority in many software-defined radio-based communications [3]. AMCs have been extensively studied in recent years [3], [4], and several Deep Learning (DL) based techniques have emerged with huge Convolutional Neural Network (CNN) layers that have shown remarkable accuracy for automatically classifying modulated radio signals [5]. While these networks offer good accuracy, CNN-based networks are intrinsically slow due to the high computational complexity of the convolution operation. Since achieving fast classification times is crucial in several wireless communications applications, it is challenging to implement CNN-based AMCs for practical purposes. The complexity of the convolution operation can be greatly reduced if it is performed in parallel. Therefore, hardware accelerators based on FPGAs perform much better than traditional CPUs for CNN inference due to their parallel

processing capabilities [6], [7]. Furthermore, with the recent advancements in FPGA technologies, FPGAs also emerged as potential candidates for AI hardware acceleration. Extensive research in this field has led to many new technologies in this space and frameworks such as *Vitis AI* have emerged, which enable AI inference acceleration on Xilinx FPGA platforms.

Vitis AI supports deep learning frameworks like TensorFlow and offers a suite of tools and APIs to prune, quantize, optimize, and compile pre-trained models to achieve the highest AI inference performance on Xilinx FPGAs [8]. In this paper, we propose a CNN-based hardware accelerator for AMC. We use the Vitis AI Development Kit, which relies on the Deep learning Processing Unit (DPU) at its core to accelerate inference for CNN-based models. The main contributions of this paper are

- Training and deploying a CNN-based AMC on the ZCU104.

- A model that achieves high classification accuracy even for low SNRs (≤ +6 dB).

- Speed and accuracy comparison of the FPGA implementation against a CPU-based edge device (Raspberry Pi).

The rest of the paper is organized as follows. Section II describes the related work. The problem statement is given in Section III and data set generation and training details are discussed in Section IV. Section V and Section VI discuss the DPU and the Vitis AI development flow. Finally, the results of our hardware implementation and conclusions are discussed in Section VII and Section VIII, respectively.

#### II. RELATED WORK

Several ML-based techniques have been proposed for AMCs using radio signals in the last few years. For instance, In [10], Tridgell et al. proposed a real-time implementation on ZCU111 using the *radioML* data set for SNRs  $\geq +6$  dB and achieved an accuracy of nearly 80% in the best case scenario (+30 dB SNR), a throughput of 488K classifications/s, and a classification latency of 8  $\mu$ s. Similarly, in [5], Kumar et al. have also proposed a real-time implementation on the ZCU111 RFSoC—achieving a 94.46% maximum accuracy on the 24-class RadioML data set at +30 dB SNR while delivering a high throughput of 527K classifications/s, and a classification latency of just 7.5  $\mu$ s. In [11], the authors have implemented a classifier for two modulation types, BPSK and QPSK, and achieved a classification accuracy of 100% for both at 10 dB SNR with a fast classification time of 42 *ns*. The definition of time to classify differs across

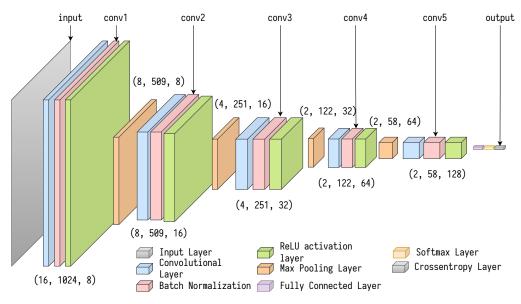

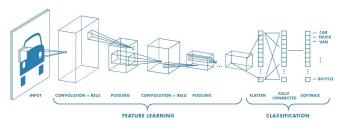

Fig. 1: Illustration of the CNN architecture used [9].

papers, with real-time implementations using latency to denote the time taken to classify the signal once the data is received. In [6], the authors achieved approximately 90% accuracy when the SNR was  $\geq +4$  dB and the classification time was 20  $\mu$ s for four modulation schemes BPSK, QPSK, 8-PSK, and 16-QAM. In [7], Soltani et al. have also worked on a real-time RF signal classification using Zynq UltraScale+ XCZU9EG FPGA and achieved a classification time of  $24\,\mu s$ , with an average accuracy of 94% over six modulation schemes; however, the SNRs used were not reported. In [12], Liu et al. also used a CNN model trained on the radio ML data set to achieve an accuracy of 72.5% for 0 dB SNR with a classification time of 4ms. Our proposed hardware classifier implements the CNN architecture proposed by Yakkati et al. [9], with ReLU activations instead of tanh, in which a total of 9 modulation schemes [BPSK, QPSK, 64-QAM, PAM4, GFSK, CPFSK, B-FM, DSB-AM, SSB-AM] are used. The accelerator is implemented on the ZCU104 using Xilinx's DPU IP, a programmable engine dedicated to accelerating convolutional neural networks. Our classifier achieved the best classification accuracy of 96%, with a throughput of 1.8K classifications/s and a classification time of 550  $\mu$ s. It is to be noted that the classification time includes the time delta to transfer the data from memory on the board through the on-chip ARM processor to the FPGA. The proposed work outshines previous implementations by a good margin even for low SNR radio signals, and achieves a modest classification speed.

#### **III. PROBLEM STATEMENT**

In the past, several AMCs were implemented using deep convolutional neural networks, and one such implementation which uses Fixed Boundary Range Empirical Wavelet Transform (FBREWT) and deep CNN is shown in Fig. 1. The CNN model comprises of five convolution layers, six batchnormalization layers, four max-pooling layers, one fully con-

nected layer, as presented in Fig. 1. The input layer accepts pre-processed data which takes the shape of  $16 \times 1024$  matrix, and the output layer is a  $9 \times 1$  vector, which corresponds to the number of modulation schemes used for classification. Such deep neural networks can be deployed on edge computing devices like the Raspberry Pi. However, CNNs heavily depend on the convolution operation, which can be tedious to evaluate on pure CPUs due to their sequential nature of execution. When evaluated in parallel, this operation can be significantly speed up; therefore, FPGAs are among the best hardware platforms for implementing CNNs. Furthermore, modulation classifiers have not been implemented that fare well for low SNR radio signals. This work proposes a method to implement the CNNbased classifier that achieves high accuracy even for low SNR radio signals. The proposed method uses the Vitis AI tools provided by Xilinx to port the CNN model on Zynq FPGA to achieve hardware acceleration. Finally, we compare the performance metrics of the inference times with a raspberry pi 4B, which is an edge device with an ARM CPU.

#### IV. DATA SET, PREPROCESSING AND TRAINING

Table I summarizes the modulation schemes to be classified and the SNRs used in this work. A sizeable data set is necessary to attain good accuracy post-training. Therefore, for each signal-to-noise ratio, MATLAB was used to generate 9000 unique modulated signals (1000 signals per modulation scheme) by varying the AWGN channel levels between -4 dB to 10 dB.

TABLE I: Modulation types and signal-to-noise ratios used

| Modulation Schemes | BPSK,QPSK, 64-QAM, PAM4, GFSK, CPFSK,<br>B-FM, DSB-AM, SSB-AM |

|--------------------|---------------------------------------------------------------|

| SNRs               | 10, 8, 6, 4, 2, 0, -2, -4                                     |

Then for each modulated signal, 16 sub-band signals (1024 samples in size) were generated by passing the modulated signal through the pre-processor discussed in section IV-A, which are then stacked together to form a  $16 \times 1024$  image-like matrix, which the CNN receives as the input.

#### A. Empirical Wavelet Transform

*Empirical Wavelet Transform* (EWT) allows a multi-scale analysis of a time domain signal using an adaptive wavelet subdivision scheme. The EWT starts with segmenting the signal's spectrum and provides a perfect reconstruction of the input signal. The EWT coefficients partition the energy of the input signal into separate pass-bands [13].

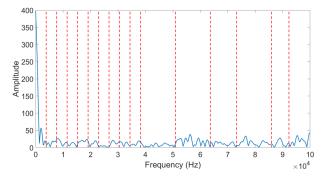

Fig. 2: Boundaries applied on the frequency spectrum [9].

In this work, we used Fixed Boundary Range EWT (FBREWT), where the frequency boundaries of the filter banks in the Fourier domain are pre-initialized, which means that regardless of the modulation scheme, the applied filter banks remain the same. Before creating the final data sets for training, the generated signals for each modulation scheme are pre-processed using FBREWT. We then perform the Fourier domain analysis on every modulated signal, extracting the subbands with the help of adaptive wavelet filter banks. For a given radio signal

$$r_n = [r(n)]_{n=0}^{N-1} \tag{1}$$

where N is the length of the radio signal, the Fourier domain signal is given by

$$R_k = \sum_{n=0}^{N-1} r_n \cdot \exp\left(j\frac{2\pi}{N}kn\right) \tag{2}$$

where k is the frequency at which the Fourier spectrum is evaluated, and it will be within the range  $[0, f_s/2]$  where  $f_s$  is the sampling frequency of the signal. In the referred work [9], 16 pre-initialized filter banks are applied in the range  $[0, \pi]$ segmented at  $\mathbf{B}_l = [0.12, 0.24, 0.36, 0.48, 0.60, 0.72, 0.84,$ 0.96, 1.08, 1.20, 1.6, 2.0, 2.3, 2.7, 2.9], which corresponds tothe following frequency segment array

$$\mathbf{F}_l = \frac{\mathbf{B}_l}{2\pi} f_s \tag{3}$$

Filter banks are applied for each of the 16 segments in  $\mathbf{F}_l$ , as shown in Fig. 2, to extract the sub-band signals using the

Inverse Discrete Fourier Transform (IDFT) and trim each subband signal to 1024 samples. Thus, a  $16 \times 1024$  sub-band matrix is generated after pre-processing. The final matrix for each modulation scheme for a given SNR is appended together to form a  $9000 \times 16 \times 1024$  array and then saved it in Matlab as a .mat file, which can be later imported to TensorFlow.

#### B. Training

The models were implemented for each SNR ratio in TensorFlow and the pre-processed data sets saved from MATLAB were imported in Python and fed to the CNN. Keras is used for network description and training and testing stages. Sklearn library was used to split the data set containing 9000 images into the training and testing data sets using the train\_test\_split function. This function takes x, y, and  $test\_size$  as inputs. It returns x\_train, y\_train, x\_test, and y\_test as outputs, where x is the input image data array of 9000 images with each image of size  $16 \times 1024 \times 1$ , and y is an output labels array representing the modulation class corresponding to each element in x. The data set is split in a 9:1 ratio with the *test\_size* chosen to be 0.10; therefore, the  $x_{train}$  and  $x_{test}$  contain 8100 and 900 images, respectively. Similarly, y\_train and y\_test contain 8100 and 900 labels, respectively. Training was performed for 100 epochs with a batch size of 128 per iteration using Google Colab, and each model took approximately 20 minutes to reach saturation in the validation accuracy.

#### V. DEEP LEARNING PROCESSING UNIT

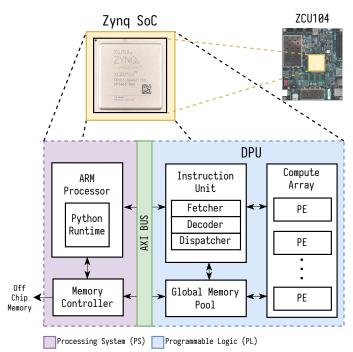

Xilinx's DPU is a programmable engine optimized for convolutional neural networks. The unit includes a highperformance scheduler module, a hybrid computing array module, an instruction fetch unit module, and a global memory pool module. The DPU uses a specialized instruction set, which efficiently implements many convolutional neural networks. Some convolutional neural networks deployed include VGG, ResNet, GoogLeNet, YOLO, SSD, MobileNet, and FPN, among others. The DPU IP can be implemented in the Programmable Logic (PL) of the selected Zynq-7000 SoC or Zynq UltraScale+ MP-SoC device with direct connections to the Processing System (PS). The DPU requires instructions to implement a neural network and accessible memory locations for input and temporary and output data. A program running on the Application Processing Unit (APU) is also required to service interrupts and coordinate data transfers [14].

#### A. DPU Architecture

The internal architecture of the DPU consists of a scheduler module, processing engines (PEs), an instruction unit block, and a global memory pool module, see Fig. 3. The APU is the ARM processor on which the application will run, serves interrupts and data transfer from and to the DPU. The instruction unit handles reading and executing the instructions associated with the different operations of the accelerated CNN [16]. The *Fetcher*'s primary role is to fetch the DPU instructions associated with the model from memory. The decoder is responsible for decoding the instructions to drive the PEs. The dispatcher

Fig. 3: ZCU104 Zynq UltraScale+ MPSoC evaluation board showing PS, PL, and internal architecture of DPU [15].

manages the data/instructions transfer among the PEs and the memory. The Global Memory Pool acts as a buffer for the input and output data and intermediate output from the DPU, which results in high throughput [16]. DPU is configurable and exposes several parameters which can be specified to optimize PL resources or customize enabled features. The DPU can be configured to meet the demands of a specific CNN architecture, which is why the DPU outshines other development flows. Xilinx's tools that are provided for configuring the DPU offer a lot of flexibility in choosing the framework (such as Tensorflow, Caffe and PyTorch), and the development flow uses the Vitis AI docker image, which contains all the necessary libraries to generate the instructions for the DPU.

#### VI. VITIS AI FRAMEWORK

The Vitis AI development environment accelerates AI inference on Xilinx hardware platforms, including edge devices and Alveo accelerator cards. It consists of optimized IP cores, tools, libraries, models, and example designs. It is designed with high efficiency and ease of use in mind, unleashing the the full potential of AI acceleration on Xilinx FPGAs. It makes it easier for users to develop deep-learning inference applications by abstracting away the intricacies of the underlying FPGA.

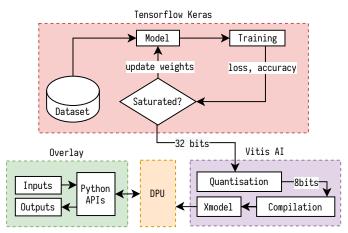

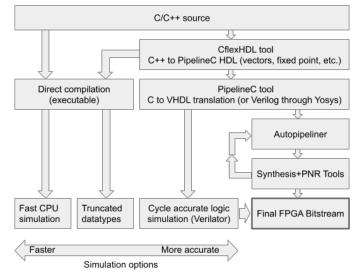

The development flow is described in Fig. 4; the model is first trained in the TensorFlow framework using the data set generated from MATLAB. Training epochs are repeated until the validation loss and accuracy reach a saturation point, after which the model weights (which are in 32-bit floating point format) are exported to a file in *hdf5* format. The Vitis AI tools provide a model quantizer that supports all major frameworks,

and it is used to convert the 32-bit floating point weights to 8-bit fixed point representation. This process uses a small calibration data set (in our case, it contains 900 samples) to minimize the accuracy loss due to a reduction in the model weight precision. After the quantization stage, the model is passed to the Vitis AI compiler, which converts the model graph to a set of domain specific instructions for the DPU unit; these instructions are saved to an *Xmodel* file which is loaded at run time. During inference, a Python script running on the APU acts as the mediator between the PS and PL; the script transfers the data from the on-chip memory to the DPU memory buffers. The DPU executes the instructions and the output classification vector is received in the Python run time. The details about the quantizer and compiler are briefly discussed in the next section.

#### A. Vitis Quantizer

In the context of DL, quantization is the process of representing the model weights in a smaller number of bits which reduces the numerical precision of the network, its complexity, and memory footprint, consequently resulting in reduced energy and storage costs [17]. Efficient quantization results in reduction in the overall model file size while mitigating the loss in accuracy. The Vitis AI quantizer relies on the *AdaQuant* [17] algorithm, which consumes a small calibration data set from training data without over-fitting and converts the numerical representation of the model weights from 32-bit floating point to 8-bit fixed point representation.

#### B. Vitis Compiler

The domain-specific compiler that comes with Vitis AI converts the quantized model into the appropriate sequence of instructions that drive the DPU. This is accomplished by identifying each layer and converting it into equivalent instructions. By the end of such a process, the main goal is to generate the kernels that shall be deployed on the FPGA and then used by API functions provided to drive the accelerators [16]. In this work, the Vitis AI compiler compiles the classification model after quantizing them into 8-bit fixed-point representation, which is the default post-quantization size.

#### C. Vitis API and Overlays

Overlays are hardware libraries that extend the user application from the PS into the PL. Overlays can accelerate a software application or customize a hardware platform for a particular application. For example, image processing is a typical application where the FPGAs can provide acceleration. We can use an overlay similar to a software library to run some of the image processing functions on the FPGA fabric. Similarly, the DPU can be considered an overlay that can be called from the PS using Vitis APIs to accelerate convolution layers on the PL. Initially, the data is stored in the off-chip memory, controlled by the DDR-controller through the AXI-Bus.

Model description in the off-chip memory is loaded onto the on-chip DPU buffers as a part of configuring the DPU for acceleration. Once the DPU finishes a process, the data is taken

Fig. 4: Development flow to convert the model from Tensor-Flow to hardware implementation.

from the output on-chip buffers back to memory for any desired post-processing. The data includes the model input image, with a size of  $16 \times 1024$ , the model weights and biases, and model-associated instructions. The main objective of the Vitis API functions is to configure the DPU for the CNN model desired to be accelerated, which includes reading the DPU instruction sequence of the model and loading weights in the DPU [16]. Moreover, the API functions handle the data exchange between the CPU and the DPU, which allows the data to be preprocessed before being fed to the DPU or post-processed after carrying out the inference, which the DPU accelerates.

#### VII. RESULTS

The CNN model was trained in TensorFlow to get similar accuracy as the MATLAB implementation described in the paper [9]. Table II depicts the accuracy comparison between the MATLAB and the TensorFlow implementations; we can observe that the accuracy is comparable; the 6 dB and 8 dB SNR take  $a \le 2\%$  dip in accuracy, whereas the rest are within  $\pm 1\%$  range.

TABLE II: Comparison of obtained from the referred work with TensorFlow implementation

| SNR(dB) | MATLAB(tanh) [9] | TF2(tanh) |

|---------|------------------|-----------|

| 10      | 96.44            | 95.91     |

| 8       | 96.89            | 95.49     |

| 6       | 93.56            | 90.34     |

| 4       | 89.11            | 87.21     |

| 2       | 82.22            | 81.93     |

| 0       | 73.11            | 74.44     |

| -2      | 63.78            | 64.56     |

| -4      | 59.56            | 61.87     |

The referred CNN model in [9] uses *tanh* activation functions. However, Xilinx's DPU does not support tanh activation function; therefore, the model had to be retrained using *ReLU* activation functions which posed quite a challenge since the

TABLE III: Accuracy comparison for each SNR values across different implementations

| SNR  | S                | oftware     |           | Hardware       |

|------|------------------|-------------|-----------|----------------|

|      | Imple            | ementations |           | Implementation |

| (dB) | MATLAB(tanh) [9] | TF2(tanh)   | TF2(ReLU) | DPU(ReLU)      |

| 10   | 96.44            | 95.91       | 97.22     | 94.44          |

| 8    | 96.89            | 95.49       | 96.67     | 96.00          |

| 6    | 93.56            | 90.34       | 93.56     | 92.78          |

| 4    | 89.11            | 87.21       | 89.11     | 85.44          |

| 2    | 82.22            | 81.93       | 80.89     | 79.69          |

| 0    | 73.11            | 74.44       | 73.56     | 69.33          |

| -2   | 63.78            | 64.56       | 66.67     | 63.11          |

| -4   | 59.56            | 61.87       | 60.00     | 54.89          |

| Avg  | 81.83            | 81.46       | 82.21     | 79.46          |

learning rate at which the model reached saturation for tanh activation is different from ReLU. So a new learning rate scheduler had to be implemented that exponentially reduces the learning rate with the number of training epochs. Table III shows that the TensorFlow ReLU implementation is better than the TensorFlow tanh implementation and matches the MAT-LAB results from the referred paper. However, since the DPU implementation uses the quantized 8-bit weights, the model took a significant hit to the accuracy for  $\pm 4$  dB and -2 dB SNR with  $\leq 5\%$  dip in accuracy. Still, the other SNRs were within a 2% range. The average classification accuracy for the DPU implementation was 79.46% which is not that far from the 81.83% average accuracy in the referred paper.

#### A. DPU Performance and Resource Utilization

The DPU is connected to the ARM processor through an AXI bus on the FPGA chip to manage task scheduling and offloading weights and data to the DPU. AXI bus carries data and weights to the DPU. The DPU power consumption and resource utilization are optimized by leveraging special *UltraRAM* slices. The UltraRAM is a novel memory solution by Xilinx, which introduces higher memory speed with low energy consumption and resource utilization on the ZCU104 with the DPU, indicating that running the DPU on the fabric is quite a resource-intensive task.

#### B. FPGA vs CPU Performance

Perhaps the most exciting part of the current work is analyzing the performance against an edge device that is CPU only. For this purpose, a Raspberry Pi model 4 was chosen, which contains a Quad core Cortex-A72 (ARM v8) 64-bit SoC @ 1.5GHz and 4 GB of RAM. The TensorFlow model was slimmed down using TensorFlow Lite and the inference metrics were extracted from both the CPU (with all four cores utilized) and the DPU implementations, which are summarized in Table V and Table VI, respectively. From the results, we can observe that the classification times per sample on the Raspberry Pi comes out to be around 24.5/900 = 0.0272s, whereas the on the DPU it is approximately 0.5/900 = 0.00055s. This roughly translates to a speed boost of  $50 \times$  the time taken by a quad core ARM CPU.

| TABLE IV: DPU resource | utilisation on | the ZCU104 board. |

|------------------------|----------------|-------------------|

|------------------------|----------------|-------------------|

| Metric               | LUT    | LUT As Mem | Registers | BRAM   | URAM  | DSP Slices |

|----------------------|--------|------------|-----------|--------|-------|------------|

| Total Resources      | 227696 | 101516     | 456485    | 308    | 96    | 1728       |

| Used by DPU          | 103171 | 11224      | 199093    | 290    | 92    | 1380       |

| Resource Utilisation | 45.31% | 11.06%     | 43.61%    | 94.16% | 95.83 | 79.86      |

TABLE V: Metrics on Raspberry Pi for validating 900 samples.

| SNR(dB) | Throughput (FPS) | Time   | Accuracy |

|---------|------------------|--------|----------|

| 10      | 36.32            | 24.777 | 97.22    |

| 8       | 37.54            | 23.971 | 96.67    |

| 6       | 37.51            | 23.988 | 93.44    |

| 4       | 36.97            | 24.344 | 89.11    |

| 2       | 37.05            | 24.286 | 80.89    |

| 0       | 36.24            | 24.830 | 73.56    |

| -2      | 37.63            | 23.911 | 66.67    |

| -4      | 36.67            | 24.542 | 60.00    |

#### VIII. CONCLUSIONS

In this paper, we proposed Xilinx's DPU-based hardware accelerator for an automatic modulation classifier based on FBREWT and deep CNN using the ZCU104 FPGA. A total of eight SNRs and nine modulation schemes were used (six digital modulation signals [BPSK, QPSK, 64-QAM, PAM4, GFSK, CPFSK] and three analog modulation signals [B-FM, DSB-AM, SSB-AM]). The details about data set generation in MATLAB and pre-processing were discussed briefly. The model weights were quantized from a 32-bit floating point representation to 8-bit fixed point representation with an accuracy loss margin of 5%. The model was compiled using the Vitis AI framework, which accepts TensorFlow model and generates instructions for configuring the DPU. Python APIs were used to transfer the data between the DPU and ARM chip on the Zynq SoC. The proposed accelerator could achieve an average classification accuracy of 79.46%, with the highest accuracy of 96.00%. It was successfully demonstrated that our FPGA hardware accelerator outperforms with respect to classification time when compared to the tflite model running on the Raspberry Pi containing the quad-core ARM CPU. The proposed accelerator was observed to perform reasonably well at low SNRs ( $\leq +6$  dB) compared to similar works. The accelerator achieves a  $50 \times$  boost in classification speed compared to the CPU implementation using Raspberry Pi having a quad core Cortex-A72 (ARM v8) 64-bit SoC @1.5GHz. A throughput of 1.8K classifications/sec could be achieved with  $550 \, \mu s$  per classification.

#### REFERENCES

- [1] Z. Zhu and A. K. Nandi, Automatic modulation classification: principles, algorithms and applications. John Wiley & Sons, 2015.

- [2] O. Dobre, A. Abdi, Y. Bar-Ness, and W. Su, "Survey of automatic modulation classification techniques: classical approaches and new trends," *IET Communications*, vol. 1, pp. 137–156(19), April 2007.

- [3] T. Huynh-The, Q.-V. Pham, T.-V. Nguyen, T. T. Nguyen, R. Ruby, M. Zeng, and D.-S. Kim, "Automatic modulation classification: A deep architecture survey," *IEEE Access*, vol. 9, pp. 142 950–142 971, 2021.

TABLE VI: Metrics on the ZCU104 for validating 900 samples.

| SNR(dB) | Throughput (FPS) | Time   | Accuracy |

|---------|------------------|--------|----------|

| 10      | 1769.86          | 0.5085 | 94.44    |

| 8       | 1802.72          | 0.4992 | 96.00    |

| 6       | 1786.66          | 0.5037 | 92.78    |

| 4       | 1799.79          | 0.5001 | 85.44    |

| 2       | 1790.78          | 0.5026 | 79.69    |

| 0       | 1798.87          | 0.5003 | 69.33    |

| -2      | 1765.70          | 0.5097 | 63.11    |

| -4      | 1792.02          | 0.5022 | 54.89    |

|         |                  |        |          |

- [4] S. A. Ghunaim, Q. Nasir, and M. A. Talib, "Deep learning techniques for automatic modulation classification: A systematic literature review," in 2020 14th International Conference on Innovations in Information Technology (IIT), 2020, pp. 108–113.

- [5] S. Kumar, R. Mahapatra, and A. Singh, "Automatic modulation recognition: An fpga implementation," *IEEE Communications Letters*, pp. 1–1, 2022.

- [6] A. F. De Castro, R. S. R. Milléo, L. H. A. Lolis, and A. A. Mariano, "Artificial neural network based automatic modulation classification system applied to fpga," in 2021 34th SBC/SBMicro/IEEE/ACM Symposium on Integrated Circuits and Systems Design (SBCCI), 2021, pp. 1–6.

- [7] S. Soltani, Y. E. Sagduyu, R. Hasan, K. Davaslioglu, H. Deng, and T. Erpek, "Real-time and embedded deep learning on fpga for rf signal classification," in *MILCOM 2019 - 2019 IEEE Military Communications Conference (MILCOM)*, 2019, pp. 1–6.

- [8] V. Kathail, "Xilinx vitis unified software platform," in Xilinx Vitis Unified Software Platform, ser. FPGA '20. New York, NY, USA: Association for Computing Machinery, 2020, p. 173–174. [Online]. Available: https://doi.org/10.1145/3373087.3375887

- [9] R. R. Yakkati, R. R. Yakkati, R. K. Tripathy, and L. R. Cenkeramaddi, "Radio frequency spectrum sensing by automatic modulation classification in cognitive radio system using multiscale deep cnn," *IEEE Sensors Journal*, vol. 22, no. 1, pp. 926–938, 2022.

- [10] S. Tridgell, D. Boland, P. H. Leong, R. Kastner, A. Khodamoradi, and Siddhartha, "Real-time automatic modulation classification using rfsoc," in 2020 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), 2020, pp. 82–89.

- [11] M. Keshk and K. Asami, "Fpga-based automatic modulation recognition system for small satellite communication systems," 2017.

- [12] X. LIU, J. SHANG, P. H. Leong, and C. LIU, "Modulation recognition using an fpga-based convolutional neural network," in 2019 22nd International Conference on Electrical Machines and Systems (ICEMS), 2019, pp. 1–6.

- [13] J. Gilles, "Empirical wavelet transform," *IEEE Transactions on Signal Processing*, vol. 61, no. 16, pp. 3999–4010, 2013.

- [14] A. Xilinx. (2019) Zynq dpu v3.1. AMD Xilinx. [Online]. Available: https://docs.xilinx.com/v/u/3.1-English/pg338-dpu

- [15] J. Zhu, L. Wang, H. Liu, S. Tian, Q. Deng, and J. Li, "An efficient task assignment framework to accelerate dpu-based convolutional neural network inference on fpgas," *IEEE Access*, vol. 8, 2020.

- [16] A. S. Hussein, A. Anwar, Y. Fahmy, H. Mostafa, K. N. Salama, and M. Kafafy, "Implementation of a dpu-based intelligent thermal imaging hardware accelerator on fpga," *Electronics*, vol. 11, no. 1, 2022. [Online]. Available: https://www.mdpi.com/2079-9292/11/1/105

- [17] I. Hubara, Y. Nahshan, Y. Hanani, R. Banner, and D. Soudry, "Improving post training neural quantization: Layer-wise calibration and integer programming," *CoRR*, vol. abs/2006.10518, pp. 2–3, 2020. [Online]. Available: https://arxiv.org/abs/2006.10518

- [18] A. Xilinx. (2016) Ultraram: Breakthrough embedded memory integration on ultrascale + devices; technical report wp477. AMD Xilinx. [Online]. Available: https://docs.xilinx.com/v/u/en-US/wp477-ultraram

# FPGA Implementation of Staggered Cellular Automata for Wave Propagation Simulation

Gustavo O. Pereira\*, Santiago Guzman-Anaya<sup>†</sup>, Henrique G. Moura<sup>‡</sup> and Daniel M. Muñoz<sup>\*†</sup>

\*Faculty of Gama, Electronics Engineering Undergraduate Program

<sup>‡</sup>Faculty of Gama, Automotive Engineering Undergraduate Program

<sup>†</sup>Department of Mechanical Engineering, Mechatronics Graduate Program, Automation and Control Group/GRACO

University of Brasilia, Brasilia, DF, Brazil

Email:gustavo.galvao@aluno.unb.br, santiago.anaya@aluno.unb.br, hgmoura@unb.br, damuz@unb.br

Abstract—The simulation of acoustic phenomena using a system resolution by ordinary PDEs is a work that demands a high computational cost. Using the phenomenon of propagation of acoustic waves in an ideal elastic medium in a steady state, it is possible to use a cellular automata system to simulate the phenomena. Even implementing a hardware solution using CA, the computational cost to simulate very large meshes is high. This work proposes a hardware architecture for a onedimensional staggered cellular automata system model based on hybrid cells that can represent the basic wave phenomena. The proposed hybrid cell guarantees the simulation of different types of meshes without having to remodel the circuit. The proposed one-dimensional staggered cellular automata was able to successfully simulate 187 cells using a block composed of ten cells. The proposed solution enables the simulation of large meshes using FPGA devices with few resources.

*Index Terms*—Cellular Automata, FPGA, Floating-point Arithmetics, Hardware-Software Co-design.

#### I. INTRODUCTION

A partial differential equation (PDE) is a mathematical relation that may involve two or more partial derivatives of an undefined function. These kinds of equations are widely used in engineering modelings, because of their faithful representation of physical phenomenons [11]. However, the computational solution of PDEs is a hard numerical task and a time-consuming process [16].

Sound propagation is an engineering problem that can be stated in many physical situations and projects. Sound wave propagation can be described by the second law of motion of physical systems and, because of that, it is not easy to handle. Firstly, in practical simulations, the wave interacts with the involved complex geometries in space. Secondly, the wave equation that describes the sound wave propagation is a parabolic PDE, describing a time-dependent phenomenon [7].

In acoustic modelings, the PDEs need to consider many details on discrete signal processing, in addition to other application issues. Thus, working with PDEs may be useful for simple and small structure modelings, only.

Cellular automata (CA) modeling can be used to reduce the computational cost needed to solve PDEs. This numerical modeling approach considers a system of artificial cells that brings, inside their units, a very simple set of mathematical rules and well-defined states. In the case of sound propagation, in an ideal elastic medium and steady state, the well-known d'Alembert solution, applied to the one-dimensional wave movement, can be used to describe all the CA basic rules.

Recently, a hardware architecture of a CA was developed and implemented on FPGA devices, being able to emulate the basic wave phenomenons in one-dimensional systems [10]. The proposed organisms use three different cells to model dispersion, generation and hybrid mechanisms, and the results showed that the CA model fits the analytical solution. However, considering that each cell must represent a very small, and fixed piece of the studied environment, the authors stated that the solution may suffer with limited resources on the chip [9].

To overcome the above problem, this work presents a staggered solution for CA and proposes a hardware architecture for FPGA implementation. The staggered approach allows CA organisms to be divided into several pieces, called blocks of cells, that emulate wave propagation phenomena by using only the current state and the past state of each cell and its neighbors until the whole desirable calculation of the physical system is performed. The proposed approach can be implemented on small FPGA devices, in order to cover large physical systems.

In addition, this work proposes a generic cell for wave propagation in one dimension and its respective hardware implementation. The generic CA can be used to cover all the basic wave phenomenons, simplifying the hardware implementation of artificial organisms and improving the staggered approach efficiency.

Cellular automata and their implementation strategies have been recently studied for simulating different physical phenomena. An FPGA implementation of the popular CA system, called "the Conway's game of life" was implemented in [1] achieving an acceleration factor of 36,7 times than an equivalent GPU (*Graphic Processing Units*) application and, 2908 times faster than a traditional CPU solution.

The work presented by [14], brings an adaptive CA approach to the wave propagation problem, in two-directional space. The obtained results were compared to numeric and analytical models, available in the specific literature, with good convergence. A CA emulation of seismic events was implemented on a super-computer, obtaining results that exceed previous software simulated applications [5]. Another contribution was presented by [6] which developed a CA

system to emulate structure-borne noise in one, two, and threedimensional cases. The results pointed out a good convergence to the specific literature applied to the problem, which means that a new strategy becomes useful to the mentioned problem.

Jiménez-Morales *et al.* presented an alternative CA solution to the traditional PDEs model for laser's dynamic [4]. There were proposed variants to the traditional models, applied to different kinds of lasers. The obtained results were quantitatively validated for many real scenarios. The work presented by [2] brings a CA model able to emulate a ruptured biological diaphragm. The model was experimentally validated in a nontrivial problem.

Table I summarizes the related works using CA models. It can be seen, in the mentioned works, that only one is focused on the modeling of wave phenomenons propagation problems, considering its basic interactions with the obstacles in space. However, the obtained implementation holds some limitations related to the number of cells that could be parallelized in hardware, and, as a consequence, limits the size of the emulated physical system.

| Authors             | Year | Kind of solution              | Plataforms |

|---------------------|------|-------------------------------|------------|

| Bakhteri, Cheng,    | 2020 | A SoC implementation of       | FPGA       |

| and Semmelhack      |      | a CA system for the Con-      |            |

| [1]                 |      | way's game of life.           |            |

| Shafiei, Khaji, and | 2020 | Adaptive CA system ap-        | CPU        |

| Eskandari-Ghadi     |      | plied to sound wave propa-    |            |

| [14]                |      | gation in an elastic lossless |            |

|                     |      | bidimensional case.           |            |

| Lin and Zhao [5]    | 2020 | Seismic events modeling       | Super-     |

|                     |      | using CA systems.             | computer   |

| Luo, Wang, and      | 2021 | A CA modeling applied to      | CPU        |

| Lei [6]             |      | the emulation of structure-   |            |

|                     |      | borne noises.                 |            |

| Jiménez-Morales,    | 2018 | Presentation of an alterna-   | CPU        |

| Guisado, and        |      | tive CA model applied to      |            |

| Guerra [4]          |      | laser's dynamics.             |            |

| Gupta, Gözen, and   | 2019 | CA system to emulate          | CPU        |

| Taylor [2]          |      | a ruptured biological di-     |            |

|                     |      | aphragm.                      |            |

| Moura and Muñoz     | 2021 | SoC implementation            | FPGA       |

| [10]                |      | of a CA model to              |            |

|                     |      | emulate acoustic wave         |            |

|                     |      | phenomenons in one-           |            |

|                     |      | dimensional space.            |            |

#### TABLE I State of art

#### II. BACKGROUD

#### A. Digitalized d'Alembert's Solution

Considering a plane wave propagating in the x direction, the propagation equation is [3]

$$\frac{\partial^2 p(x,t)}{\partial t^2} - \frac{1}{c_0^2} \frac{\partial^2 p(x,t)}{\partial t^2} = 0 \tag{1}$$

Manipulating this equation, it is possible to describe a solution based on the addition of two concurrent wave plots at any point in space [8] as follows,

$$p = f(x - c_0 t) + g(x + c_0 t)$$

(2)

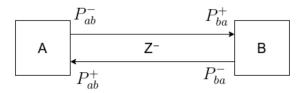

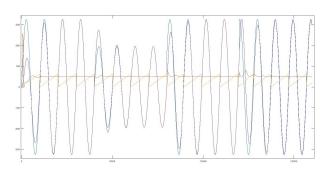

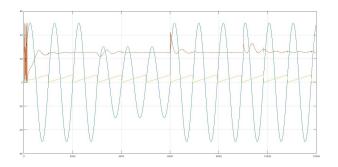

This equation is known as d'Alembert's solution to the onedimensional acoustic wave equation. Figure 1 represents the digitization of d'Alembert's solution for one-dimensional wave propagation. Notice that the sound pressure p(n) is the sum of the plots  $p^+(n)$  and  $p^-(n)$ , where n is the instant of time.

Fig. 1. Digitized d'Alembert solution for the one-dimensional wave. The output signal of point A is the input signal of point B, and vice versa [9].

Considering a generalized case where the waves can come from N different directions, the sound pressure at point J is calculated by

$$p_J = \sum_{i=1}^{2N} p_i^+ \psi_i,$$

(3)

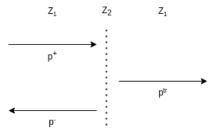

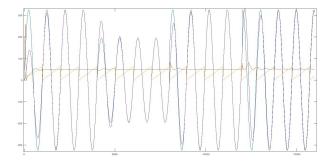

where  $p_i^+$  is the input sound pressure coming from direction i and  $\psi_i$  is the transmission coefficient. This equation is the mathematical model that will be used for the development of the CA model, as it represents the digitized d'Alembert solution for the one-dimensional wave. Figure 2 shows how the wave transmission and reflection phenomena occur within a medium of impedance  $Z_1$  with an obstacle of impedance  $Z_2$ . In the figure,  $p^+$  represents the portion incident on the obstacle,  $p^-$  as the portion reflected by the obstacle, and  $p^{tr}$  as the portion transmitted through the obstacle.

Fig. 2. Transmission and reflection of plane wave in a one-dimensional space. When passing through an obstacle, a part of the signal  $p^+$  is reflected, and the other part  $p^{tr}$  is transmitted.

Considering that the characteristic impedance (R) of the medium can be determined by the ratio between sound pressure and the particles velocity, and assuming that the transmitted energy and the reflected energy are equal to the incident energy, the transmission coefficient can be stated as,

$$\psi_i = \frac{2R_i}{R_J + \sum_{i=1}^{2N} R_i}$$

(4)

Combining the equations 4 and 3, the solution to the onedimensional wave transmission problem is obtained as,

$$p_J = \frac{2R_1}{R_1 + R_2} p_{right}^+ + \frac{2R_1}{R_1 + R_2} p_{left}^+, \tag{5}$$

where  $R_J$  is the characteristic impedance in the joint J,  $R_i$  is the characteristic impedance of the front (point A) and rear (point B) joints, and  $p_{right}^+$  and  $p_{left}^+$  are the pressure on the right and left, respectively.

#### B. Camphs1D System

The cellular automata system *Camphs1D* (*Cellular Automata Modeling of One-dimensional Physical Systems*) was proposed and implemented in [10]. This model implements the phenomena of one-dimensional wave propagation and reflection using a CA system.

To develop this system, three types of cells were modeled considering the wave physics phenomena: a) a dispersion cell that transmits the signal that comes from its neighboring cells (eq. 6); b) a generation cell that generates a signal and transmits it to its neighboring cells (eq. 7); and c) a hybrid cell that receives a signal and transmits and reflects part of this signal (eq. 8). The symbols "+" and "-" represent propagation direction,  $\alpha_r$  and  $\alpha_t$  are the reflection and transmission coefficients, n is the time constant, and p is the pressure.

It is worth mentioning that, although in a strictly physical sense the term "dispersion" represents velocity and frequency changes, we maintained the terminology and formulation of the digital waveguides stated in [15], in which the term "dispersion" was coined for the propagation of acoustic waves.

#### III. GENERIC ONE-DIMENSIONAL CELL MODEL

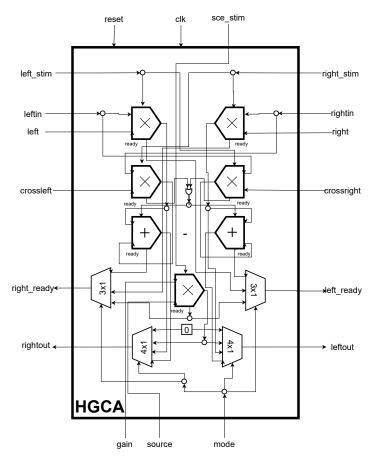

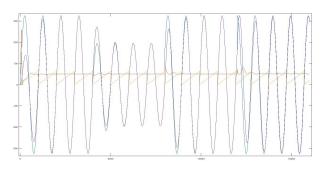

The proposed cells represent a new cell model for all the functions implemented in [10]. In order to facilitate the implementation of complex CA systems, this work presents a hybrid cell hardware architecture, named HGCA, that behaves like any of the three cells (see Fig. 3). Deriving an equation from the architecture is not straightforward because the architecture mixes the behavior of three cells by using muxes that enable the evaluation of the necessary conditions to select the required behavior (dispersion, generation, or hybrid).

The HGCA cell consists of 5 floating-point multipliers, 2 floating-point adders, 2 3x1 multiplexers, 2 4x1 multiplexers, 1 OR logic gate, and 6 buffers signal. It has 14 input signals and 4 output signals of different sizes. The floating-point arithmetic representation was used to provide a large dynamic range if

Fig. 3. Generic cell structure implemented in reconfigurable hardware. The HGCA cell is composed of 5 multipliers, 2 adders and 4 multiplexers.

compared to fixed-point, allowing very small and very large numbers to be represented with the same bit-width [13].

Comparing the structure of the HGCA cell proposed in Fig. 3 with cells reported in [10], it is noted that the HGCA cell has more floating-point operations; however, it provides the flexibility of choosing which mechanism the cell will follow at each time instant.

Looking at the latency of each mode that the cell can operate, it can be noticed that a hybrid cell has the highest time consumption with 4 clock cycles. Both dispersion and generator cells, have a latency of 2 clock cycles, causing a delay in the system when a hybrid cell acts together with the others. Thus, some buffers were used to delay the *ready* signals in the faster modes. From this, the default latency time for this cell model is 4 clock cycles.

#### IV. PROPOSED STAGGERED ARCHITECTURE

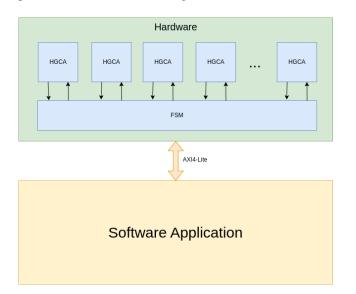

This architecture allows the cellular automata simulation to be divided into blocks of cells. Thus, small FPGA devices with fewer resources can simulate larger wave propagation systems.

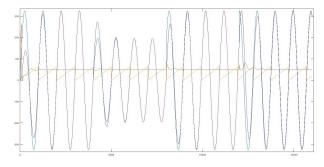

Figure 4 depicts the proposed staggered cellular automata. The main idea is to have a separate block of cells communicating with a software application. The cell block represents the structure where the cells are stored and the application sends to each cell the mode of operation, and the neighbors' current and past states. The maximum number of cells that can be stored in the block depends on the logical resources assigned. The application block could be implemented in software with a processor or in hardware using a Finite State Machine.

Fig. 4. Staggered architecture reference model with the generic cells. The communication is directly with the cell block.

In this work the staggered architecture was implemented in VHDL using floating point arithmetic operation IP-Cores, previously developed [13], [12]. Using the *FOR GENERATE* directive, it was possible to develop a parameterized solution for the number of cells the block can implement.

This cellular automata system emulates acoustics behaviors considering a homogeneous medium, i.e the same characteristics in all directions, and thin rigid walls that only produce reflections. Changes in the propagation medium were not considered in this work; however, a cellular automata system can implement this situation by adapting the distance between two neighboring cells (the higher the density, the closer the particles of the propagation medium). The distance between two consecutive cells can be implemented with registers that emulate the time delays representing the length between the cells. It is important to highlight that analytical methods, such as digital wave guides [15], commonly use the same sampling frequency and, as a consequence, only homogeneous mediums can be studied.

For comparison purposes, the same artificial organism *Camphs1DB9G2* proposed in [10] was used, allowing the response obtained by the staggered and non-staggered solutions to be compared. The organism Camphs1DB9G2 uses 187 cells, 3 hybrids, 2 generators, and the remainder are dispersion cells. The hybrid cells are at positions 2, 130, and 186. The first generator cell is at position 43 and operates for 16-time intervals, then changes to dispersion mode. The second generator cell is at position 93 and operates for 8-time intervals, then changes to dispersion mode. For the generator cells, two sinusoidal signals were created according to the

sampling frequency of the system. In the staggered solution, the cell block was implemented with 10 parallel HGCA cells.

Testbenches with reading and writing capabilities were developed to test the proposed architecture. *Octave* scripts were developed to automatically get the text files from the generator cells.

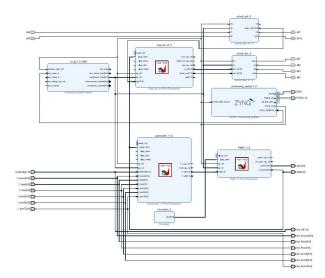

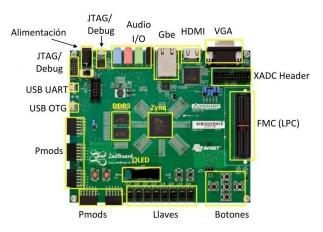

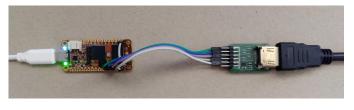

For the physical implementation of the one-dimensional staggered cellular automata system model, two main components are needed: the cell block to calculate the outputs of each cell and a software application, which would be in charge of controlling the cell block inputs and modes of operations. In this work a hardware-software co-design was developed to integrate the cell block to the ARM processor of a Zynq 7020 System on Chip (SoC) device using the AXI4-Lite protocol. Thus, the information about the cells is controlled by the ARM processor. Using this principle, the mesh size limitation simulated by the FPGA will be associated with the memory size of the processor.

#### V. RESULTS

#### A. Resources Occupation as a Function of the Bit-width

A numerical accuracy study with the proposed HGCA cell was done taking into account the bit-width of the exponent and mantissa words of the floating-point representation. The considered values for the mantissa word were 11, 13, 16 and 18 bits while the bit-width of the exponent word changed between 6 and 8 bits. For each proposed combination, the consumption of LUTs, FFs, DSPs and BRAM were collected after logic synthesis using Vivado and the Zynq 7020 SoC device from Xilinx. Table II shows the result obtained after the logic synthesis process for each of the cases.

TABLE II

HARDWARE OCCUPATION OF THE HYBRID CELL.

|               | Bits | LUT  | FF  | DSP | BRAM |

|---------------|------|------|-----|-----|------|

| EXP:8 FRAC:18 | 27   | 1125 | 314 | 5   | 0    |

| EXP:8 FRAC:16 | 25   | 884  | 292 | 5   | 0    |

| EXP:8 FRAC:13 | 22   | 740  | 259 | 5   | 0    |

| EXP:8 FRAC:11 | 20   | 683  | 237 | 5   | 0    |

| EXP:6 FRAC:18 | 25   | 1086 | 296 | 5   | 0    |

| EXP:6 FRAC:16 | 23   | 819  | 274 | 5   | 0    |

| EXP:6 FRAC:13 | 20   | 687  | 241 | 5   | 0    |

| EXP:6 FRAC:11 | 18   | 617  | 219 | 5   | 0    |

A significant reduction in the consumption of LUTs and FFs was observed when the bit-width of the mantissa reduces from 18 to 16 bits. When decreasing the number of bits of the mantissa, the reduction still occurs, but in a smaller size. The reduction in the exponent size did not generate a significant change in the consumption of LUTs but had a slight reduction in the consumption of FFs.

For the sake of numerical comparisons with previous works, we decided to implement the proposed HGCA cell and the staggered CA architecture using a 27-bit floating-point representation (8 bits for the exponent word and 18 bits for the mantissa word).

#### B. Resource Occupation of the HGCA Cell

The generic HGCA cell proposed in Fig. 3 was encapsulated with an AXI4-Lite interface, to validate its physical implementation on a Xilinx Zynq 7020 FPGA SoC with a clock frequency of 100 MHz. Table III shows the resource utilization of the generic cell, with a consumption of 1119 LUTs, 303 FFs and 5 DSPs.

TABLE III RESOURCE UTILIZATION OF THE HGCA CELL

|   | Resource | Estimated | Available | Utilization% |

|---|----------|-----------|-----------|--------------|

|   | LUT      | 1119      | 53200     | 2,10         |

| . | FF       | 303       | 106400    | 0,28         |

|   | DSP      | 5         | 220       | 2,27         |

|   | BRAM     | 0         | 140       | 0            |

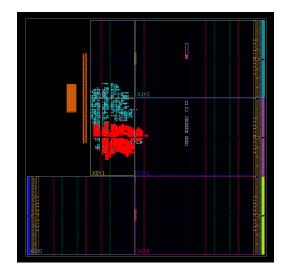

Figure 5 shows the circuit layout after the Place and Route process. In red is shown the occupation of slices by the HGCA cell. In blue, are shown the AXI4-Lite interface and other modules. One can conclude that it is possible to scale the number of cells in the Zynq 7020 device, as will be presented in the following subsection.

#### C. Characterization of the Staggered Cellular Automata

The validation of the proposed staggered CA architecture was carried out through behavioral simulations and from the physical implementation of a block of 10 HGCA cells using a Zynq 7020 SoC device at a clock frequency of 100 MHz.

Initially, the VHDL description of the artificial organism Camphs1DB9G2 (consisting of 187 cells) was validated in behavioral simulation using TXT files with memory values of each cells of the block at different positions and time instants.

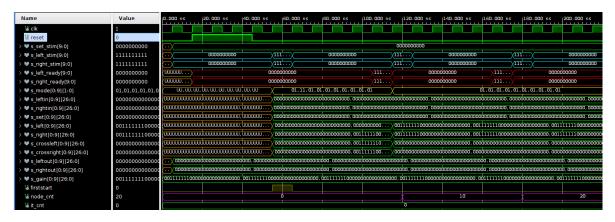

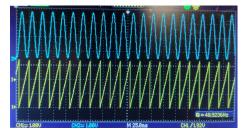

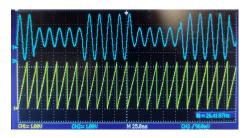

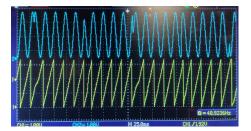

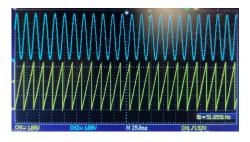

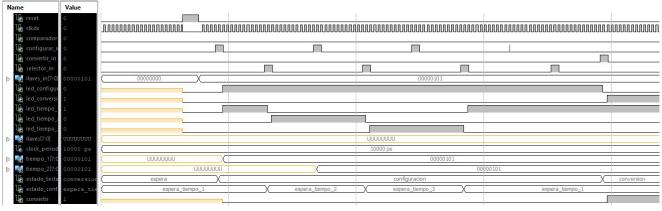

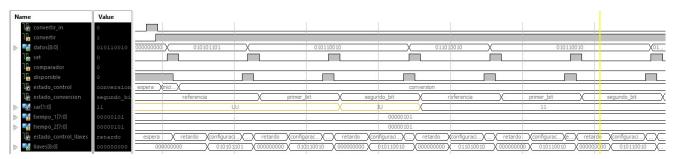

Figure 6 shows the initialization of the simulation. Notice that the *firststart* signal initializes the simulation and, from here, the system starts reading new inputs into the cells when

Fig. 5. The result obtained from PAR (*Place and Route*) after implementing the cell together with the ARM processor. In red is the region of logical blocks occupied by the HGCA cell. In cyan is the rest of the logical blocks occupied by the solution. In orange is the space occupied by the ARM processor.

the cell block finishes calculating the outputs of the simulated cells. Over the course of the simulation, it can be noticed that the number of cells simulated at each time instant is increasing 10 by 10 with the *node\_cnt* signal (in magenta). When simulating 187 cells at each time instant, the iteration counter is incremented ( $it_cnt$ ). The simulation continues until 160-time iterations are completed.

During the simulation, the output values of a cell block were stored in a TXT file, which was used as input for the cell blocks in the next iteration. These files were also used to visualize and validate the output of the architecture from a script in *Octave*. For visualization purposes, the results of the outputs of each cell were summed left and right. With this result, a video was generated showing the outputs obtained from the proposed staggered architecture (https://youtu.be/BZG6xB7996U).

To simulate the required 160-time cycles of the 187 cells, 182.46  $\mu s$  were required, thus achieving a throughput of 0.877 MOPS, whereas the non-staggered hardware architecture achieved a throughput of 25 MOPS [10]. On the other hand, the non-staggered solution, for the same system implemented in C (GCC compiler), required 0.7128 s running on the ARM processor and 0.1138 s for an AMD Ryzen7 3700U, 17.8GB RAM, Linux Mint 20.3.

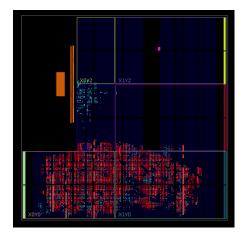

Figure 7 shows the result of the staggered architecture mapped on a Zynq 7020 device. The proposed circuit was effectively mapped on the FPGA device using a clock frequency of 100 MHz. Table IV shows a resource utilization of the proposed architecture for the Camphs1DB9G2 system. A comparison with our previous work [10], which does not fit on the Zynq 7020 device, demonstrates that the proposed staggered dramatically reduces the resource occupation.

TABLE IV RESOURCE UTILIZATION OF THE STAGGERED SOLUTION.

| Architecture       | Platform | LUTs  | FFs   | DSPs | BRAMs |

|--------------------|----------|-------|-------|------|-------|

| Staggered          | Z7020    | 12361 | 5877  | 50   | 2     |

| (Total)            | Zedboard |       |       |      |       |

| Staggered          | Z7020    | 11052 | 3030  | 50   | 0     |

| (block cells)      | Zedboard |       |       |      |       |

| Non-staggered      | ZU7EV    | 22422 | 21924 | 372  | 0     |

| (block cells) [10] | ZCU104   |       |       |      |       |

The energy consumption of the staggered solution for a clock frequency of 100 MHz was approximately 0.142 W of static power and 1.565 W of dynamic power, being 96% of the dynamic power dissipated by the ARM processor.

#### VI. CONCLUSIONS

This work proposed a one-dimensional staggered cellular automata system to simulate acoustic wave propagation phenomena. The proposed solution is based on a generic cell structure that emulates the dispersion and reflection wave propagation mechanisms in a one-dimensional space. The model was able to simulate larger systems with fewer computational resources if compared to the previous solution in [10].

A hardware-software co-design was proposed for the integration of the staggered cellular automata system with an

Fig. 6. Behavioral simulation result of the staggered solution with blocks of 10 cells for the Camphs1DB9G2 system. In cyan the left and right start signals, in red the ready signals, in yellow the mode signals, and in magenta the counter with the number of simulated cells.

Fig. 7. Result obtained from PAR (*Place and Route*) after implementing the cell block with AXI4-Lite and the ARM processor. In red, there is the region of logical blocks occupied by the block of HGCA cells. In cyan, we have the rest of the logical blocks occupied by the solution. In orange, we have the space occupied by the ARM processor.

ARM processor. Thus, when integrating the processor with the DDR memory present in the development kit, the solution would be limited to the size of the DDR memory and not to the on-chip BRAM memory, which is always a scarce resource. This solution allows the simulation of thousands of cells, without being limited by the resources of the FPGA device.

As future works, we intend to replace the ARM processor with a Microblaze soft-processor, allowing a considerable reduction in energy consumption. It is also expected to develop a staggered cellular automata model in two dimensions, allowing real simulations of acoustic phenomena to be accelerated. Additionally, we intend to model wave phenomena using internal registers between the cells allowing different frequencies and propagation speeds to be emulated.

#### REFERENCES

Rabia Bakhteri, Julian Cheng, and Alex Semmelhack. Design and implementation of cellular automata on FPGA for hardware acceleration. *Procedia Computer Science*, 171:1999–2007, 2020. Third International Conference on Computing and Network Communications (CoCoNet'19).

- [2] Abhay Gupta, Irep Gözen, and Michael Taylor. A cellular automaton for modeling non-trivial biomembrane ruptures. *Soft Matter*, 15:4178–4186, 2019.

- [3] D.E. Hall. Basic Acoustics. Krieger, 1993.

- [4] Francisco Jiménez-Morales, José Luis Guisado, and José Manuel Guerra. Simulating Laser Dynamics with Cellular Automata, pages 405–422. Springer International Publishing, Cham, 2018.

- [5] Zhe Lin and Xiaohua Zhao. An improved approach to simulate seismic events based on cellular automata. *International Journal of Modern Physics C*, 31(04):2050053, 2020.

- [6] Kun Luo, Zhenguo Wang, and Xiaoyan Lei. The cellular automata model of sound propagations and its application in structural noise calculations. *Applied Acoustics*, 182:108262, 2021.

- [7] Friedrich Moser, Laurence J. Jacobs, and Jianmin Qu. Modeling elastic wave propagation in waveguides with the finite element method. NDT & E International, 32(4):225–234, 1999.

- [8] H. Moura. Simulação da propagação de ondas acústicas através de uma malha de guias digitais de ondas., 2006. Disssertação (Mestrado em Engenharia Mecânica), UFU, Uberlândia, Brasil.

- [9] H. Moura. Implementação em chip de sistemas celulares autômatos dedicados à emulação da propagação de ondas acústicas em sistemas físicos., 2022. Monografia (Bacharel em Engenharia Eletrônica), UnB, Brasilia, Brasil.

- [10] Henrique G. Moura and Daniel M. Muñoz. Modeling wave propagation using cellular automata on chip. In 34th IEEE Symposium on Integrated Circuits and Systems Design (SBCCI), pages 1–6, 2021.

- [11] G.M. Murphy. Ordinary Differential Equations and Their Solutions. Van Nostrand, 1960.

- [12] Daniel M Muñoz, Diego F. Sanchez, Carlos H. Llanos, and Mauricio Ayala-Rincón. FPGA based floating-point library for CORDIC algorithms. In 2010 VI Southern Programmable Logic Conference (SPL), pages 55–60, 2010.

- [13] Daniel M. Muñoz, Diego F. Sanchez, Carlos H. Llanos, and Mauricio Ayala-Rincón. Tradeoff of FPGA design of a floating-point library for arithmetic operators. volume 5, pages 42–52, Journal Integrated Circuits and Systems, 2010.

- [14] Masoud Shafiei, Naser Khaji, and Morteza Eskandari-Ghadi. An adaptive cellular automata approach with the use of radial basis functions for the simulation of elastic wave propagation. *Acta Mechanica*, 231(7):2723–2740, 2020.

- [15] Julius O Smith. Physical modeling using digital waveguides. Computer music journal, 16(4):74–91, 1992.

- [16] Holger Thies. Uniform computational complexity of ordinary differential equations with applications to dynamical systems and exact real arithmetic. Graduate School of Arts and Sciences, University of Tokyo, Tokyo, Japan, 2018.

# Streamlining FPGA Circuit Design and Verification with Python and *py4hw*

David Castells-Rufas, Gemma Rotger Universitat Autònoma de Barcelona (UAB) Cerdanyola del Vallés, Spain 0000-0002-7181-9705, 0000-0002-9538-5278

Abstract—Classic hardware design languages, such as VHDL and Verilog, were born more than 30 years ago to improve the productivity of circuit design offered by manual schematic drawing. Over the years, the effort of Digital Hardware Design has shifted from circuit design to circuit verification. Although classic HDLs have been extended to adapt to this changing scenario, they have a hard time to cope with the complexity demanded at the design and verification stages. Radical changes incorporating high-level software programming languages in the design and verification processes seem inevitable. Accordingly, many new HDL proposals are already based on Python. In this paper, we present a novel Python-based HDL framework that tries to address some of the limitations of current Python-based HDLs with a special focus on verification and education.

Index Terms-FPGA, Verilog, Python

#### I. INTRODUCTION

The Python programming language has become very popular in the scientific community due to its simplicity, crossplatform support, easy learning curve, and a multitude of existing and ever-increasing functionality that is easily distributed through Internet-based setup infrastructures like PyPi and Conda. Hardware design languages (HDLs) like VHDL and Verilog were born as domain-specific languages to address the productivity limitations of manual schematic drawing. Modern digital circuits are generally designed using a compositional methodology, where circuits are subdivided into simpler interconnected blocks. This division is repeated until simple enough circuits, which are part of the platform primitives, are obtained.

The benefit of using a domain-specific language was justified when Object-Oriented (OO) languages were not mainstream, and it was not easy to express the compositional structure of hardware with them. Now, General-Purpose Programming Languages (GPPLs) can easily describe complex circuit descriptions by instantiating smaller blocks. The evolution of HDLs has moved the attention to the circuit verification features of the languages. We argue that, instead of trying to transform the domain-specific HDLs into GPPLs, it makes more sense to complement existing GPPLs to be able to describe Hardware blocks and provide a simulation infrastructure that allows complex verification. Several proposals have followed this approach. To name a few: SystemC [1] based on C/C++, JHDL [2] based on Java, and Chisel [3] based on Scala. We believe that some roadblocks hinder their David Novo Laboratoire d'informatique, de robotique et de microélectronique de Montpellier (LIRMM) Montpellier, France 0000-0002-5510-4152

wide adoption. While Java is still popular in the business domain, it is not so popular among the scientific and electrical engineering communities. Also, even with the relative success of Chisel, Scala is not a very popular language. On the other hand, while C/C++ is very popular in the scientific and electrical engineering communities, the language suffers from some limitations (e.g. poor introspection) that makes it less attractive to become the center of an HDL framework.

Despite the well-known performance limitations, Python still offers some compelling features to be the base of an HDL framework. There have been several proposals based on Python in the literature [4]–[9], but, they lack some features like visualization, interactive simulation, and, in some cases, they have an unclear separation between hardware design styles. These features are part of our proposed framework py4hw and could be incorporated into some of the other Python-based tools. As part of our commitment to the Open Hardware movement [10] and to improve education in Digital Hardware Design, we have made our tools available on both GitHub and PyPI under the GPL 3.0 license. We believe in the importance of open access to tools and resources for the advancement of the field, and we hope that our contributions will support the broader community of hardware designers and educators.

The organization of the paper is as follows: In Section II, we describe the main aspects of the py4hw framework. Special focus is given to the flexibility aspects of the framework in Section III and the visualization features in Section IV. Section V details the verification features of the framework. We describe the strength of the framework for education in section VI. Before concluding, Section VII analyzes related work and compares it with the current proposal.

#### II. py4hw

The functionality base of Python is far superior to that available in Verilog/SystemVerilog. Hence, using Python in *py4hw* provides an excellent foundation for elaborating complex hardware, defining of simulation stimuli, and developing verification testbenches. *py4hw* is specially optimized for the design of synchronous digital circuits, and it is influenced by JHDL [2].

The evolution of hardware design has consolidated three main design styles:

- Structural: description of blocs and their connections

- Register transfer level (RTL): description of the response of circuits at certain events (signal activation or clock edge)

- Sequential: Description of processes using a Von-Neumann-like approach where actions occur by the execution of an algorithm

Many Python-based HDLs mix design styles (as Chisel also does) or use non-intuitive methods to create hardware circuits, introducing unnecessary confusion to the designer. *py4hw* aims to differentiate between design styles and avoid language constraints that limit the freedom to create any circuit.

py4hw follows and Object Oriented (OO) design style. Every circuit (equivalent to Verilog module) is modeled by a Python class, which can be instantiated by other circuits. In Verilog, modules have two different sets of constructorarguments, a mandatory set for the input and output wires, and an optional set for module parameters. In py4hw, the only mandatory constructor-arguments are the parent circuit and the name of the instance. py4hw maintains a hierarchical object model with parent-child relations. Each circuit instance contains a link to its parent, and a dictionary of children indexed by instance name. The top-level entity of the hierarchy is the HWSystem object. Thus, circuit constructors can have an arbitrary number of additional parameters, and the interface of the circuit (inputs and outputs) is built during runtime avoiding any static interface definition. The clock is implicit. All circuits have an assigned clock driver which is normally inherited from the parent circuit. However, multiple clockdrivers can be used, and there is support for gated clocks by using a special clock-driver object.

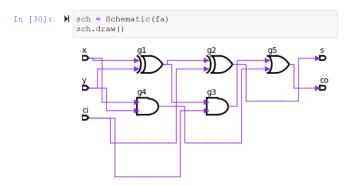

A fundamental class is the Wire class. An instance of the Wire class represents a signal that connects one source with one-or-more sinks. Wires have a width, a name, and a parent circuit that must be specified during creation. A significant difference with other HDLs is that wires are indivisible. Extracting specific bits from a wire, concatenating wires, or obtaining a range of wires from a wire require to use specific circuits. All circuits inherit from the class Logic, which provides some basic methods to create the circuit interface. Structural, RTL, and sequential design styles are supported in py4hw. The structural design style is based on the instantiation of objects from previously defined classes in the constructor of the class. The following code illustrates how to design a 1-bit Full Adder circuit with a structural design style.

```

class FullAdder(Logic):

def __init__(self, parent, name, x, y, ci, s, co):

super().__init__(parent, name)

# interface definition

x = self.addIn('x', x)

y = self.addIn('y', y)

ci = self.addIn('ci', ci)

s = self.addOut('s', s)

co = self.addOut('s', s)

co = self.addOut('co', co)

# internal wires

w1 = self.wire('w1',1)

w2 = self.wire('w1',1)

w2 = self.wire('w2',1)

w3 = self.wire('w3',1)

# instances

```

Xor2(self, 'g1', x, y, w1)

Xor2(self, 'g2', w1, ci, s)

And2(self, 'g3', w1, ci, w2)

And2(self, 'g4', x, y, w3)

Or2(self, 'g5', w2, w3, co)

*py4hw* also supports RTL design style by allowing to use the behaviour of the circuits using simple Python code. Two possible circuit types are supported: combinational and sequential. In both cases, the constructor of the class is used to define the interface and save their wires into the properties of the object. Combinational behavioral circuits must implement the propagate method. The following code illustrates how the previous Full Adder circuit can be described by using a combinational behavioural implementation.

```

class FullAdder(Logic):

def __init__(self, parent, name, x, y, ci, s, co):

super().__init__(parent, name)

# interface definition

...

def propagate(self):

v = self.x.get() + self.y.get() + self.ci.get()

self.s.put(v % 2)

self.co.put(1 if v > 1 else 0)

```

Sequential behavioral circuits are defined by implementing the clock method. The following code illustrates how to implement a simple Finite State Machine (FSM) with two states.

```

class FSM(Logic):

def __init__(self, parent, name, r):

super().__init__(parent, name)

self.r = self.addOut('r', r)

self.state = 0

def clock(self):

if (self.state == 0):

self.r.prepare(1)

self.state = 1

elif (self.state == 1):

self.r.prepare(0)

self.state = 0

```

Sequential design style can be implemented by combining Python coroutines with the implementation of clock method. With this approach, the circuit enters a coroutine on object creation which is automatically blocked after a first yield statement is reached. The clock method must call the next method of the coroutine so that the sequential process advances until the next yield statement is found. A similar approach is used in cocotb [11] and, from the programmer's perspective, is very similar to SystemC's sequential clocked processes (SC\_CTHREAD), which used sc\_wait statement instead of yield.

*py4hw* embeds a cycle-based simulator. The simulator is responsible to propagate the wire values across the circuit and update the state. Using behavioral models instead of structural ones is a known technique to speedup simulation. In the behavioral FullAdder example, the simulator requires a single method invocation to compute the outputs of the circuit. On the other hand, using structural design for the same circuit requires the invocation of the behavioural models of all its hierarchical descendants, which takes more time. Simulation time can be advanced programmatically. This can be used in combination with state analysis to perform advanced verification and visualization strategies. This strategy was used in [12] to provide a rich visualization of the the state of a RISC-V processor while executing an compiled application. Several Python libraries (pyelftools, capstone, tkiner, ...) were used to provide a rich user experience.

*pv4hw* generates Verilog from the circuit descriptions. Since the whole circuit hierarchy is maintained in memory, the RTL generation phase only has to traverse the circuit hierarchy and decide which method to apply to generate the equivalent Verilog code for each element of the hierarchy. Structural circuits are directly translated into structural Verilog code. Behaviourally modelled circuits are transpiled into Verilog. Their defining method (either propagate or clock) is analyzed using introspection to obtain the Abstract Syntax Tree (AST) of the method's source code. Several transformations are applied until the AST can be emitted as a valid Verilog. Calls to external libraries (such as NumPy) can not be used inside behavioural models that are synthesized. On the other hand, there is no restriction to use them on constructors of Structural circuits and behavioral models as simulation stimuli. Using Python's introspection eliminates the need for external libraries that would otherwise be necessary in languages like C/C++ to parse source code.

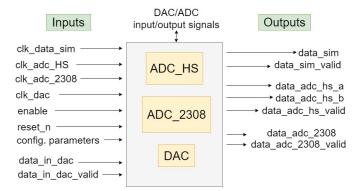

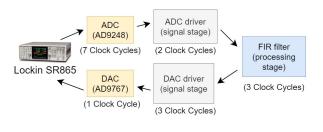

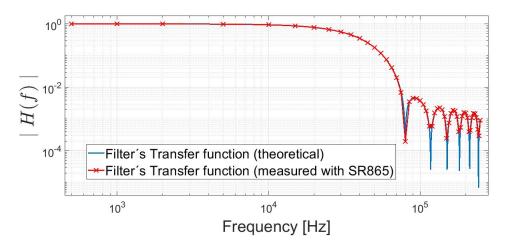

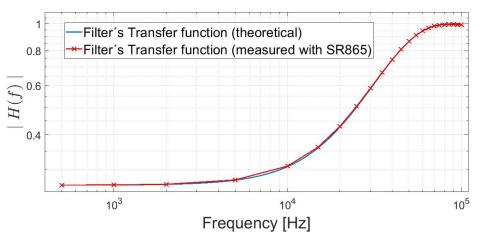

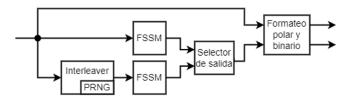

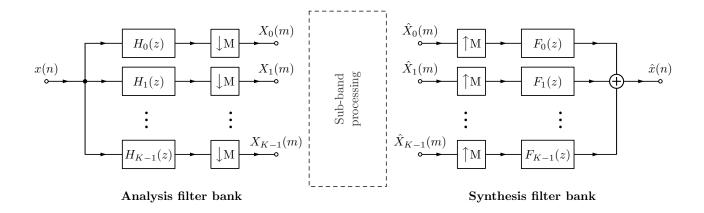

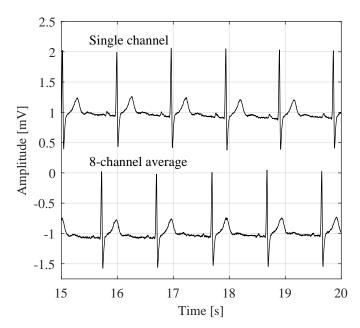

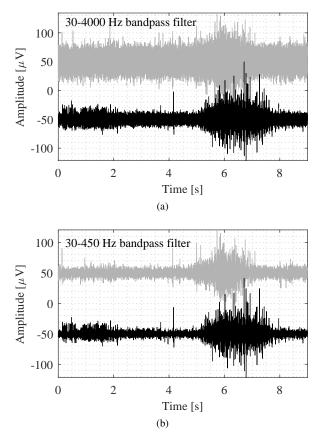

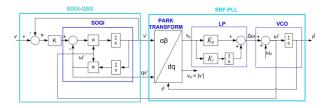

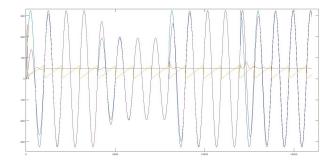

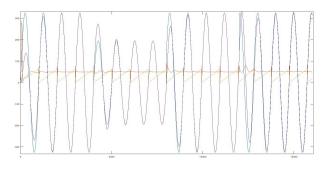

#### III. CIRCUIT FLEXIBLITY